Easy DDR4(DIMM) PCB Design(7) - Skew Constraints

각 신호끼리는 허용되는 길이 차이가 있다. 자세한 내용을 알아보자.

아래 표를 슥 봐두자.

위 표에 나온 것 처럼

각 그룹간에, 그리고 Differential 신호간에 허용되는 길이 범위가 있다.

젤 위에 Data(=DQ) 와 DQS 간 허용 오차는 ±58mil 이다. mm로는 ±1.4732mm 이다.

예를들어 만약 DQS가 100mm라면 DQ는 98.5268mm~101.4732mm 길이로 배선해야 한다는 뜻이다.

이 범위를 벗어나면 동작에 오류가 날 수 있기 때문에 이와 같은 길이 차이를 정해 놓았다.

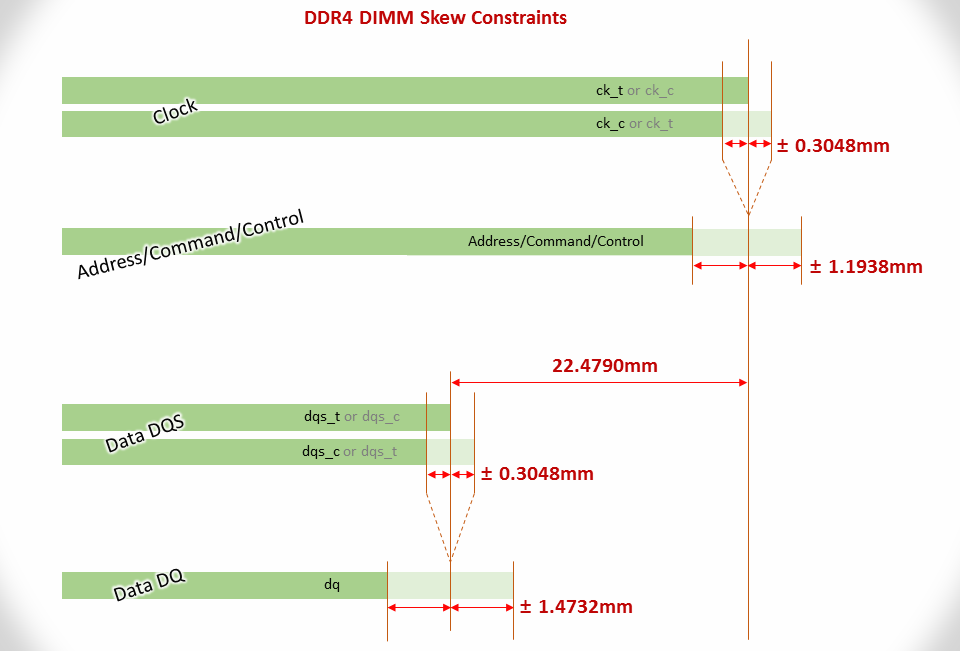

보기 쉽게 위 표를 그림으로 나타내 보았다.

Clock은 두 가닥 신호인 ck_t와 ck_c 배선 길이가 ±0.3048mm 오차범위 안에 들어와야 한다.

여기서 이 Clock 신호가 다른 신호길이에 대한 기준이 된다.

Address/Command/Control 신호는 Clock 신호를 기준으로 ±1.1938mm의 짧은 오차범위 안에 들어와야 한다.

DQS 신호는 Clock신호 보다 길거나 Clock신호보다 22.4790mm 이상 짧으면 안된다.

예를들어 Clock신호가 100mm 라고 하면

DQS신호는 77.521mm~100mm 범위 안에 배선해야 한다.

같은 100mm거나, 90mm이거나, 80mm처럼 오차범위 안에 들어와야 한다.

70mm이면 오차범위를 벗어났기 때문에 잘못된 배선이다.

그리고 DQS신호의 두 가닥 dqs_t, dqs_c 끼리의 배선길이는 ±0.3048mm 오차범위 안에 들어와야 한다.

DQ 신호는 DQS 기준으로 ±1.4732mm의 짧은 오차범위로 배선해야 한다.

여기서 추가로 알 수 있는 것은

배선길이는 간단히 두 그룹으로 나눌 수 있다는 것이다.

Clock과 Address/Command/Control이 한 그룹.

DQS와 DQ가 한 그룹이다.

그림을 보자.

위와 같이 배선 길이로만 보자면 두 그룹으로 간단히 구분할 수 있다.

Clock/Address/Command/Control을 같은 길이로 배선하고,

DQS/DQ를 같은 길이로 배선한다 생각하면 쉬워진다.

.

.

더 알아볼 것이 있다.

Data(DQS,DQ)신호는 Byte 단위로 그룹이 지정되어 있다.

그래서 배선 또한 Byte Group 단위로 길이를 맞추어야 한다.

아래 그림을 참고하자.

그림과 같이 Data신호는 Byte Group 단위로 길이를 맞추어 배선해야 한다.

물론 Clock신호 기준으로 오차범위 안에 들어와야 한다.

그리고 중요한 것 하나,

Byte Group 단위 신호들은 PCB에서 같은 층에 배선해야 한다.

예를들어 Byte Group0 에 dq0, dq1 신호가 속해 있다고 하자.

근데 dq0은 3층에 배선하고, dq1은 5층에 배선하면 안된다는 것이다.

같은 Byte Group에 속한 dqs, dq 신호는 모두 같은 층에 배선해야 한다.

그래야 신호가 더욱 정확히 전달된다.

Data 신호 뿐만 아니라 Address 신호들도 같은 층에 배선하는 것이 좋다.

.

.

정리

두가지를 알아보았다.

첫째, 각 신호들의 배선 길이 오차범위를 알아보았고,

둘째, Data 신호는 Byte Group별로 같은 길이로 같은 층에 배선해야 한다는 것을 알아보았다.

2024.05.31 수정

길이 오차범위는 약간 보완이 필요하다.

DQS는 Clock 보다 길어도 되고 짧아도 된다고 데이타시트에 명시되어 있다.

±885mil(= ± 22.4790mm)로서 플러스/마이너스 모두 표기되어 있으므로 Clock 보다 길어도 되고 짧아도 된다.

짧은 길이로만 작성했던 이유는 Clock보다 길게 배선해도 괜찮을까 하는 의문이 남아있어서 그랬었다.

'PCB 설계 > PCB설계-DDR4(DIMM) 설계' 카테고리의 다른 글

| 쉽게 배우는 DDR4(DIMM) PCB 설계(9) - 배선 이격 거리 (0) | 2020.12.31 |

|---|---|

| 쉽게 배우는 DDR4(DIMM) PCB 설계(8) - 배선 예시 (1) | 2020.12.30 |

| 쉽게 배우는 DDR4(DIMM) PCB 설계(6) - 배선 최대/최소 길이 (0) | 2020.12.28 |

| 쉽게 배우는 DDR4(DIMM) PCB 설계(5) - 배선폭 (0) | 2020.12.21 |

| 쉽게 배우는 DDR4(DIMM) PCB 설계(4) - 신호 임피던스 (0) | 2020.12.18 |